Montage Technology Lidera con Chips DDR5

Montage Technology y la Revolución de los Chips DDR5

Primera Generación de Chips de Controlador de Reloj DDR5

Montage Technology ha marcado un hito en la industria al ser la primera en probar la producción de chips de controlador de reloj DDR5 de primera generación (CKD). Este avance tecnológico ha permitido el inicio del suministro masivo a los fabricantes de memoria, marcando el comienzo de una nueva era en la velocidad y estabilidad del acceso a los datos de memoria.

Innovación en Memoria de Cliente

El chip CKD se ha diseñado para utilizarse en la nueva generación de memoria de cliente, con el fin de mejorar la velocidad y la estabilidad del acceso a los datos de la memoria. Esto es crucial para mantener el paso con la creciente velocidad operativa y el rendimiento de las CPU modernas.

Evolución de los Chips de Controlador de Reloj

En el pasado, la función del controlador de reloj se integraba en el chip del controlador de reloj registrado (RCD) para módulos RDIMM o LRDIMM de servidor. Montage Technology ha innovado al implementar esta función en el lado de la PC, lanzando varias generaciones de chips de controlador de reloj.

Hitos de Desarrollo:

-

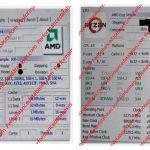

2021: Lanzamiento del chip de primera generación para soportar una velocidad de datos de 4800 MT/s.

-

2022 y 2023: Introducción de la DDR5 de segunda generación con 5600 MT/s y la tercera generación con 6400 MT/s.

-

Enero 2024: Llegada de la cuarta generación del chip RCD, compatible con DDR5 y una velocidad de datos de 7200 MT/s.

El Rol de los Chips CKD en la Memoria DDR5

Con velocidades de datos que alcanzan los 6400MT/s o más, los chips CKD se han vuelto un componente indispensable para los módulos de memoria DDR5 de clientes, como CUDIMM, CSODIMM y CAMM. Su función principal es almacenar en búfer la señal de reloj entre la CPU del cliente y la DRAM, mejorando así la integridad y confiabilidad de las señales de reloj de alta velocidad.

Cumplimiento de Estándares y Eficiencia Energética

El chip controlador de reloj DDR5 de primera generación cumple con el estándar JEDEC DDR5CKD01 y soporta velocidades de datos de hasta 7200MT/s. Ofrece acceso a direcciones de bus de banda lateral dual e interfaces I²C e I3C. Mediante registros de configuración, el chip puede ajustar las características de su señal de salida para adaptarse a la topología de red de diferentes DIMM y reducir el consumo de energía al deshabilitar señales de salida no utilizadas.

0 comentarios